단일 광자 광검출기80% 효율이라는 병목 현상을 극복했습니다.

단일 광자광검출기소형화 및 저비용이라는 장점 때문에 양자 광학 및 단일 광자 이미징 분야에서 널리 사용되고 있지만, 다음과 같은 기술적 병목 현상에 직면해 있습니다.

현재 기술적 한계

1. CMOS 및 박막 접합 SPAD: 높은 집적도와 낮은 타이밍 지터라는 장점을 가지고 있지만, 흡수층이 얇고(수 마이크로미터), 광전 변환 효율(PDE)이 근적외선 영역에 국한되어 850nm에서 약 32%에 불과합니다.

2. 후막형 SPAD: 수십 마이크로미터 두께의 흡수층을 특징으로 합니다. 시판 제품은 780nm에서 약 70%의 광검출률(PDE)을 보이지만, 80%를 돌파하는 것은 매우 어렵습니다.

3. 판독 회로의 한계: 두꺼운 접합 SPAD는 높은 애벌랜치 확률을 확보하기 위해 30V 이상의 과전압이 필요합니다. 기존 회로에서 68V의 퀜칭 전압을 사용하더라도 PDE는 최대 75.1%까지만 증가시킬 수 있습니다.

해결책

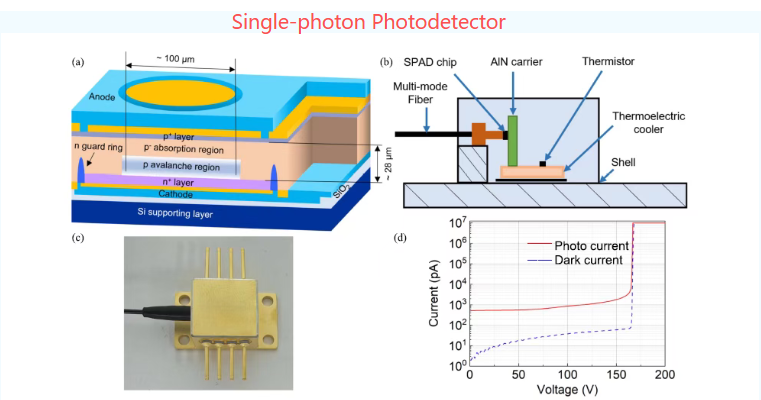

SPAD의 반도체 구조를 최적화합니다. 후면 조사형 설계: 입사 광자는 실리콘에서 지수 함수적으로 감쇠합니다. 후면 조사형 구조는 대부분의 광자가 흡수층에서 흡수되고 생성된 전자가 애벌랜치 영역으로 주입되도록 합니다. 실리콘에서 전자의 이온화율이 정공보다 높기 때문에 전자 주입은 애벌랜치 발생 확률을 높입니다. 도핑 보상 애벌랜치 영역: 붕소와 인의 연속 확산 공정을 사용하여 얕은 도핑을 보상하고 결정 결함이 적은 깊은 영역에 전기장을 집중시켜 DCR과 같은 노이즈를 효과적으로 줄입니다.

2. 고성능 판독 회로. 50V 고진폭 퀜칭, 빠른 상태 전환; 다중 모드 작동: FPGA 제어 퀜칭 및 리셋 신호를 결합하여 자유 작동(신호 트리거), 게이팅(외부 게이트 구동) 및 하이브리드 모드 간의 유연한 전환이 가능합니다.

3. 소자 준비 및 패키징. SPAD 웨이퍼 공정을 채택하고 버터플라이 패키지를 사용한다. SPAD는 AlN 캐리어 기판에 접합된 후 열전 냉각기(TEC)에 수직으로 설치되며, 서미스터를 통해 온도 제어가 이루어진다. 효율적인 결합을 위해 멀티모드 광섬유를 SPAD 중심에 정밀하게 정렬한다.

4. 성능 교정. 교정은 785nm 피코초 펄스 레이저 다이오드(100kHz)와 시간-디지털 변환기(TDC, 10ps 해상도)를 사용하여 수행되었습니다.

요약

본 연구에서는 SPAD 구조(두꺼운 접합, 후면 조사, 도핑 보상)를 최적화하고 50V 퀀칭 회로를 혁신함으로써 실리콘 기반 단일 광자 검출기의 PDE(광전 변환 효율)를 84.4%라는 새로운 최고 수준으로 끌어올리는 데 성공했습니다. 상용 제품과 비교했을 때, 종합적인 성능이 크게 향상되어 양자 통신, 양자 컴퓨팅, 고감도 이미징과 같이 초고효율과 유연한 작동이 요구되는 응용 분야에 실질적인 솔루션을 제공합니다. 본 연구는 실리콘 기반 검출기의 추가 개발을 위한 견고한 토대를 마련했습니다.단일 광자 검출기기술.

게시 시간: 2025년 10월 28일