실리콘 포토닉스 활성 소자

포토닉스 능동 소자는 빛과 물질 사이의 의도적으로 설계된 동적 상호작용을 구체적으로 지칭합니다. 포토닉스의 대표적인 능동 소자는 광 변조기입니다. 현재 실리콘 기반의 모든 광 변조기는 이러한 특성을 지니고 있습니다.광 변조기이는 플라즈마 자유 전하 운반체 효과에 기반합니다. 도핑, 전기적 또는 광학적 방법을 통해 실리콘 재료의 자유 전자와 정공의 수를 변화시키면 복소 굴절률이 변할 수 있으며, 이 과정은 1550나노미터 파장에서 Soref와 Bennett의 데이터를 피팅하여 얻은 방정식(1,2)에 나타나 있습니다. 전자와 비교했을 때, 정공은 실수 및 허수 굴절률 변화의 더 큰 부분을 유발합니다. 즉, 주어진 손실 변화에 대해 더 큰 위상 변화를 일으킬 수 있습니다. 따라서마흐-젠더 변조기링 변조기의 경우, 일반적으로 구멍을 이용하여 만드는 것이 선호됩니다.위상 변조기.

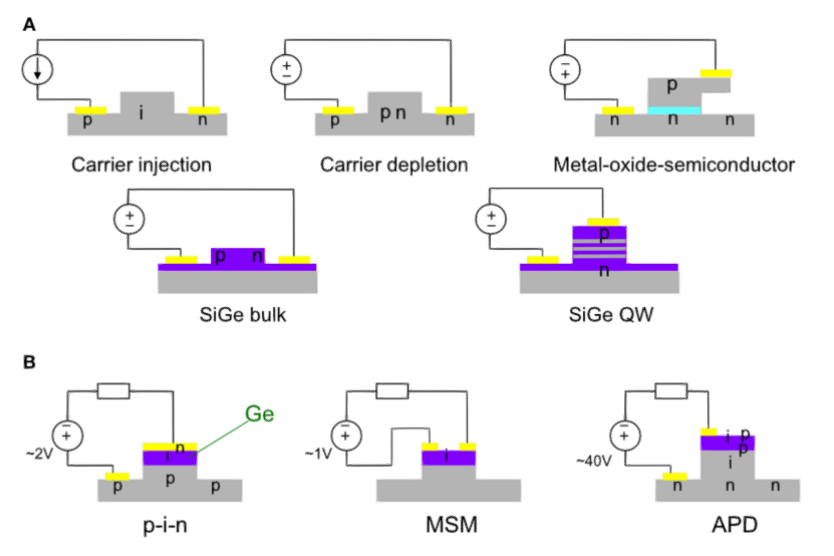

다양한실리콘(Si) 변조기그림 10A에는 다양한 유형이 나와 있습니다. 캐리어 주입 변조기에서는 빛이 매우 넓은 pn 접합 내의 진성 실리콘에 위치하고 전자와 정공이 주입됩니다. 그러나 이러한 변조기는 주입 후 자유 전자와 정공이 재결합하는 데 시간이 더 오래 걸리기 때문에 속도가 느리고 일반적으로 대역폭이 500MHz 정도입니다. 따라서 이 구조는 변조기보다는 가변 광 감쇠기(VOA)로 더 자주 사용됩니다. 캐리어 공핍 변조기에서는 빛이 좁은 pn 접합에 위치하고 pn 접합의 공핍 폭은 인가된 전기장에 의해 변화됩니다. 이 변조기는 50Gb/s 이상의 속도로 동작할 수 있지만 배경 삽입 손실이 높습니다. 일반적인 vpil은 2V·cm입니다. 금속 산화물 반도체(MOS)(실제로는 반도체-산화물-반도체) 변조기는 pn 접합에 얇은 산화막 층을 포함합니다. 이 방식은 캐리어 축적과 캐리어 고갈을 모두 허용하여 약 0.2 V·cm의 더 작은 VπL 값을 얻을 수 있지만, 광 손실이 크고 단위 길이당 정전 용량이 크다는 단점이 있습니다. 또한, SiGe(실리콘 게르마늄 합금) 밴드 에지 이동을 기반으로 하는 SiGe 전기 흡수 변조기가 있습니다. 이 외에도, 흡수성 금속과 투명 절연체 사이를 전환하는 데 그래핀을 사용하는 그래핀 변조기도 있습니다. 이러한 사례들은 고속, 저손실 광 신호 변조를 구현하기 위해 다양한 메커니즘을 활용할 수 있음을 보여줍니다.

그림 10: (A) 다양한 실리콘 기반 광 변조기 설계의 단면도 및 (B) 광 검출기 설계의 단면도.

그림 10B에는 여러 실리콘 기반 광 검출기가 나와 있습니다. 흡수 물질은 게르마늄(Ge)입니다. Ge는 약 1.6 마이크론까지의 파장에서 빛을 흡수할 수 있습니다. 왼쪽에는 현재 가장 상업적으로 성공적인 핀 구조가 나와 있습니다. 이 구조는 P형 도핑된 실리콘 위에 Ge가 성장된 형태로 구성됩니다. Ge와 Si는 4%의 격자 불일치를 가지며, 전위를 최소화하기 위해 먼저 얇은 SiGe 층을 버퍼층으로 성장시킵니다. Ge 층 위에는 N형 도핑이 수행됩니다. 가운데에는 금속-반도체-금속(MSM) 포토다이오드가, 오른쪽에는 APD(눈사태 광검출기오른쪽에 그림이 나와 있습니다. APD의 애벌랜치 영역은 Si에 위치하는데, Si는 III-V족 원소 재료의 애벌랜치 영역에 비해 잡음 특성이 낮습니다.

현재로서는 실리콘 포토닉스에 광학적 이득을 통합하는 데 있어 명확한 이점을 가진 해결책은 없습니다. 그림 11은 조립 수준별로 정리된 몇 가지 가능한 옵션을 보여줍니다. 맨 왼쪽에는 에피택시 성장된 게르마늄(Ge)을 광학적 이득 물질로 사용하는 단일체 통합 방식, 에르븀(Er) 도핑 유리 도파관(예: 광 펌핑이 필요한 Al2O3), 그리고 에피택시 성장된 갈륨비소(GaAs) 양자점을 사용하는 방식이 있습니다. 다음 열은 웨이퍼 간 조립 방식으로, III-V족 이득 영역에서 산화물과 유기물 접합을 포함합니다. 그 다음 열은 칩 간 조립 방식으로, III-V족 칩을 실리콘 웨이퍼의 공동에 삽입한 후 도파관 구조를 가공하는 방식입니다. 이 세 가지 방식의 장점은 웨이퍼를 절단하기 전에 웨이퍼 내부에서 소자의 모든 기능을 테스트할 수 있다는 것입니다. 가장 오른쪽 열은 칩 간 조립 방식으로, 실리콘 칩과 III-V족 칩을 직접 결합하는 방식뿐만 아니라 렌즈 및 회절 격자 커플러를 통한 결합 방식도 포함합니다. 상업용 애플리케이션에 대한 추세는 차트의 오른쪽에서 왼쪽으로 이동하며, 더욱 통합되고 연동된 솔루션을 지향하고 있습니다.

그림 11: 실리콘 기반 포토닉스에 광학 이득이 통합되는 방식. 왼쪽에서 오른쪽으로 갈수록 제조 삽입 지점이 공정에서 점차 뒤쪽으로 이동합니다.

게시 시간: 2024년 7월 22일